# **User Manual**

APM32F003x4x6

Arm® Cortex® -M0+ based 32-bit MCU

Version: V1.7

# Contents

| 1   | Introduction and Document Description Rules      | 6  |

|-----|--------------------------------------------------|----|

| 1.1 | Introduction                                     | 6  |

| 1.2 | Document description rules                       | 6  |

| 2   | System Architecture                              | 7  |

| 2.1 | Full Name and Abbreviation Description of Terms  | 7  |

| 2.2 | System architecture block diagram                | 7  |

| 2.3 | Memory mapping                                   | 8  |

| 3   | Flash Memory                                     | 9  |

| 3.1 | Full Name and Abbreviation Description of Terms  | 9  |

| 3.2 | Main characteristics                             | 9  |

| 3.3 | Flash memory structure                           | 9  |

| 3.4 | Flash memory functional description              | 10 |

| 3.5 | Option byte register functional description      | 13 |

| 3.6 | Register address mapping                         | 16 |

| 3.7 | Register functional description                  | 17 |

| 4   | Power Management Unit (PMU)                      | 22 |

| 4.1 | Full Name and Abbreviation Description of Terms  | 22 |

| 4.2 | Introduction                                     | 22 |

| 4.3 | Structure block diagram                          | 22 |

| 4.4 | Functional Description                           | 22 |

| 4.5 | Power Management                                 | 23 |

| 5   | Auto Wakeup (WUPT)                               | 26 |

| 5.1 | Introduction                                     | 26 |

| 5.2 | Structure block diagram                          | 26 |

| 5.3 | Functional Description                           | 26 |

| 5.4 | Register address mapping                         | 27 |

| 5.5 | Register functional description                  | 27 |

| 6   | Reset and Clock (RCM)                            | 30 |

| 6.1 | Full Name and Abbreviation Description of Terms  | 30 |

| 6.2 | Reset functional description (RMU)               | 30 |

| 6.3 | Functional description of clock management (CMU) | 32 |

| 6.4 | Register address mapping                         | 39 |

| 6.5 | Register functional description                  | 39 |

| 7   | Nested Vector Interrupt Controller (NVIC)        | 46 |

| 7.1 | Full name and abbreviation description of terms  | 46 |

| 7.2  | Introduction                                    | 46  |

|------|-------------------------------------------------|-----|

| 7.3  | Main characteristics                            | 46  |

| 7.4  | Interrupt and exception vector table            | 46  |

| 8    | External Interrupt Controller (EINT)            | 48  |

| 8.1  | Introduction                                    | 48  |

| 8.2  | Functional Description                          | 48  |

| 8.3  | Register address mapping                        | 48  |

| 8.4  | Register functional description                 | 49  |

| 9    | General-Purpose Input/Output Pin (GPIO)         | 51  |

| 9.1  | Full Name and Abbreviation Description of Terms | 51  |

| 9.2  | Main characteristics                            | 51  |

| 9.3  | Structure block diagram                         | 52  |

| 9.4  | Functional Description                          | 52  |

| 9.5  | Register address mapping                        | 53  |

| 9.6  | Register functional description                 | 54  |

| 10   | Buzzer                                          | 56  |

| 10.1 | Introduction                                    | 56  |

| 10.2 | Structure block diagram                         | 56  |

| 10.3 | Functional Description                          | 56  |

| 10.4 | Register address mapping                        | 57  |

| 10.5 | Register functional description                 | 57  |

| 11   | Timer Overview                                  | 59  |

| 11.1 | Full Name and Abbreviation Description of Terms | 59  |

| 11.2 | Timer category and main difference              | 59  |

| 12   | Advanced Timers (TMR1/TMR1A)                    | 62  |

| 12.1 | Introduction                                    | 62  |

| 12.2 | Main characteristics                            | 62  |

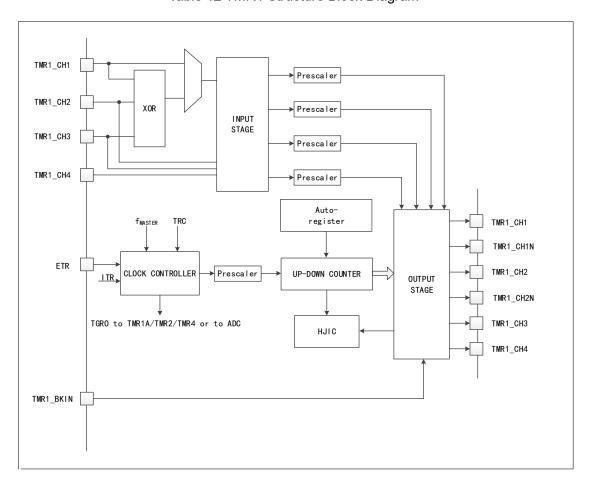

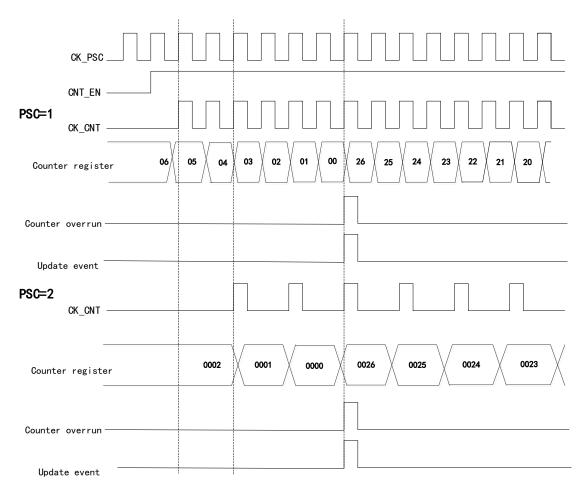

| 12.3 | Structure block diagram                         | 63  |

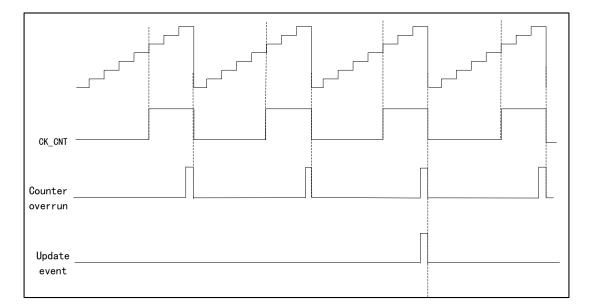

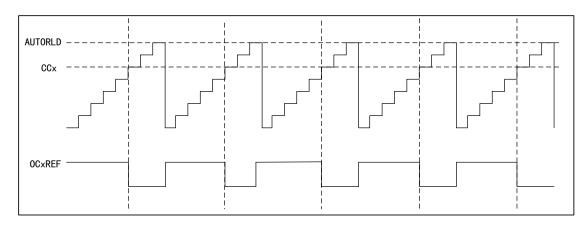

| 12.4 | Functional Description                          | 64  |

| 12.5 | Register address mapping                        | 81  |

| 12.6 | Register functional description                 | 82  |

| 13   | General-purpose Timer (TMR2)                    | 103 |

| 13.1 | Introduction                                    | 103 |

| 13.2 | Main characteristics                            | 103 |

| 13.3 | Structure block diagram                         | 104 |

| 13.4 | Functional Description                          | 104 |

| 13.5 | Register address mapping                        | 110 |

| 13.6 | Register functional description                      | 111    |

|------|------------------------------------------------------|--------|

| 14   | Basic Timer (TMR4)                                   | 123    |

| 14.1 | Introduction                                         | 123    |

| 14.2 | Main characteristics                                 | 123    |

| 14.3 | Structure block diagram                              | 123    |

| 14.4 | Functional Description                               | 123    |

| 14.5 | Register address mapping                             | 125    |

| 14.6 | Register functional description                      | 126    |

| 15   | Watchdog Timer (WDT)                                 | 130    |

| 15.1 | Introduction                                         | 130    |

| 15.2 | Independent watchdog                                 | 130    |

| 15.3 | Window watchdog                                      | 132    |

| 15.4 | IWDT register address mapping                        | 134    |

| 15.5 | IWDT register functional description                 | 134    |

| 15.6 | WWDT register address mapping                        | 135    |

| 15.7 | WWDT register functional description                 | 135    |

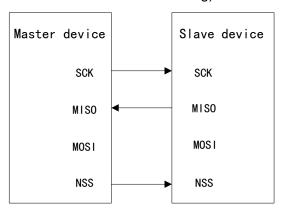

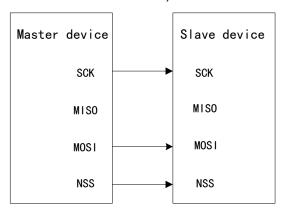

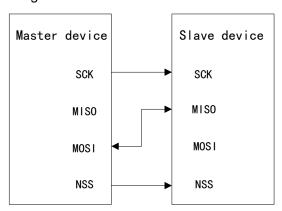

| 16   | Serial Peripheral Interface (SPI)                    | 137    |

| 16.1 | Introduction                                         | 137    |

| 16.2 | Main characteristics                                 | 137    |

| 16.3 | Structure block diagram                              | 138    |

| 16.4 | SPI functional description                           | 138    |

| 16.5 | Register address mapping                             | 147    |

| 16.6 | Register functional description                      | 147    |

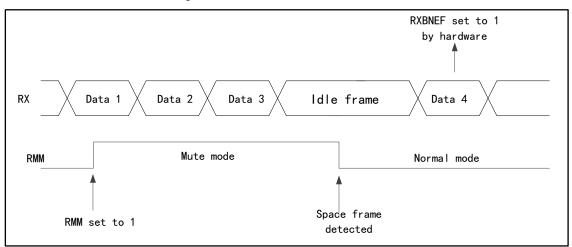

| 17   | Universal Synchronous/Asynchronous Transceiver (USAR | T) 152 |

| 17.1 | Full Name and Abbreviation Description of Terms      | 152    |

| 17.2 | Introduction                                         | 152    |

| 17.3 | Main characteristics                                 | 152    |

| 17.4 | Functional Description                               | 153    |

| 17.5 | Register address mapping                             | 164    |

| 17.6 | Register functional description                      | 164    |

| 18   | Internal Integrated Circuit Interface (I2C)          | 172    |

| 18.1 | Full Name and Abbreviation Description of Terms      | 172    |

| 18.2 | Introduction                                         | 172    |

| 18.3 | Main characteristics                                 | 172    |

| 18.4 | Structure block diagram                              | 173    |

| 18.5 | Functional Description                               | 174    |

| 18.6 | Register address mapping                             | 179    |

| 18.7 | Register functional description       | 180 |

|------|---------------------------------------|-----|

| 19   | Analog-Digital Converter (ADC)        | 188 |

| 19.1 | Introduction                          | 188 |

| 19.2 | Main characteristics                  | 188 |

| 19.3 | ADC functional description            | 189 |

| 19.4 | Register address mapping              | 192 |

| 19.5 | Register functional description       | 193 |

| 20   | Chip Electronic Signature             | 200 |

| 20.1 | Capacity register of main memory area | 200 |

| 20.2 | 96-bit unique chip ID                 | 200 |

| 21   | Version History                       | 202 |

# 1 Introduction and Document Description Rules

### 1.1 Introduction

This reference manual provides application developers with all the information about how to use MCU (micro-controller) system architecture, memory and peripherals.

For information about Arm® Cortex® -M0+ core, please refer to Arm® Cortex® - M0+ technical reference manual; please refer to the corresponding datasheet for detailed data such as model information, dimension and electrical characteristics of the device; for all MCU series models, please refer to the corresponding data manual for memory mapping, peripheral existence and their number.

### 1.2 Document description rules

### 1.2.1 Full Name and Abbreviation Description of Terms

Table 1 R/W Abbreviation and Description

| R/W                     | R/W Description                                                                                                     |       |

|-------------------------|---------------------------------------------------------------------------------------------------------------------|-------|

| read/write              | Software can read and write this bit.                                                                               | R/W   |

| read-only               | Software can only read this bit.                                                                                    | R     |

| write-only              | Software can only write this bit, and after reading this bit, the reset value will be returned.                     | W     |

| read/clear              | The software can read this bit and clear it by writing 1. Writing 0 has no effect on this bit.                      | RC_W1 |

| read/clear              | The software can read this bit and clear it by writing 0. Writing 1 has no effect on this bit.                      | RC_W0 |

| read/clear by read      | The software can read this bit, reading this bit will automatically clear it to 0, and writing this bit is invalid. | RC_R  |

| read/set                | The software can read and set this bit, and writing 0 has no effect on this bit.                                    | R/S   |

| read-only write trigger | The software can read this bit and writing 0 or 1 can trigger an event but has no effect on the value of this bit.  | RT_W  |

| toggle                  | The software can flip this bit only by writing 1, and writing 0 has no effect on this bit.                          | Т     |

# 2 System Architecture

### 2.1 Full Name and Abbreviation Description of Terms

Table 2 Full Name and Abbreviation Description of Terms

| Full name in English          | English abbreviation |

|-------------------------------|----------------------|

| Advanced High-Performance Bus | AHB                  |

| Advanced Peripheral Bus       | APB                  |

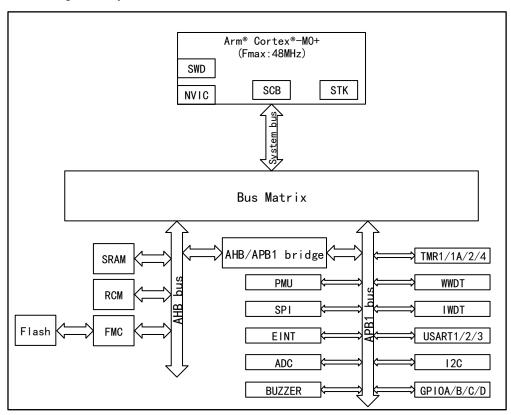

### 2.2 System architecture block diagram

The main system consists of one driving unit and three passive units. The driving unit connects the system bus (S-bus) of Arm® Cortex®-M0+ core. The three passive units are internal SRAM, internal flash memory and bridge from AHB to APB, and the bridge connects all APB devices.

These are connected through a multi-level AHB bus architecture, as shown in the figure below:

Figure 1 System Architecture of APM32F003x4x6 Series Products

Note: Different models of products contain different numbers of modules. Please refer to the data manual for details.

### 2.3 Memory mapping

The memory mapping address is totally 4GB address. The assigned addresses include the core (including core peripherals), on-chip Flash (including main memory area, system memory area and option bytes), on-chip SRAM, and bus peripherals (including AHB and APB peripherals). Please refer to the data manual of the corresponding model for specific information of various addresses.

### 2.3.1 Embedded SRAM

Built-in static SRAM. It can access by byte, half word (16 bits) or full word (32 bits). The start address of SRAM is 0x2000 0000.

### 3 Flash Memory

This chapter mainly introduces the storage structure, read, erase, write, read/write protection, unlock/lock characteristics of Flash, and the involved register functional description.

### 3.1 Full Name and Abbreviation Description of Terms

Table 3 Full Name and Abbreviation Description of Terms

| Full name in English    | English abbreviation |

|-------------------------|----------------------|

| Flash Memory Controller | FMC                  |

### 3.2 Main characteristics

- (1) Flash memory structure

- Contain main memory area and information block

- The capacity of main memory area is up to 32KB

- The information block is divided into system memory area and option byte area

- The capacity of the system memory area is 1KB, for storing 96-bit unique UID, and main memory area capacity information

- The capacity of the option byte area is 24B

- (2) Functional description

- Read Flash

- Page/Mass erase Flash

- Write Flash

- Read/White protection Flash

- Configure option bytes

# 3.3 Flash memory structure

Table 4 Flash Memory Structure of APM32F003x4x6 Series Products

| Block Name               |        | Address area            | Size (bytes) |

|--------------------------|--------|-------------------------|--------------|

| Main memory area Page 0  |        | 0x0000 0000-0x0000 03FF | 1K           |

| Main memory area         | Page 1 | 0x0000 0400-0x0000 07FF | 1K           |

| Main memory area         | Page 2 | 0x0000 0800-0x0000 0BFF | 1K           |

| Main memory area         | Page 3 | 0x0000 0C00-0x0000 0FFF | 1K           |

| Main memory area         |        |                         |              |

| Main memory area Page 31 |        | 0x0000 7C00-0x0000 7FFF | 1K           |

| Block             | Name               | Address area            | Size (bytes) |

|-------------------|--------------------|-------------------------|--------------|

| Information block | System memory area | 0x0002 0000–0x0002 03FF | 1K           |

| Information block | Option byte        | 0x0002 0400-0x0002 07FF | 24           |

Note: The number of pages in the main memory block of APM32F003x4x6 series products is related to the Flash capacity of specific product.

### 3.4 Flash memory functional description

Describe the operation of main memory and information block (including system memory area and option byte), including read, write, erase and read/write protection.

Reading Flash includes main memory block and information block, while the erase, write, read/write is introduced separately; the system memory area has been written before the product leaves the factory and cannot be modified by the user. The erase, write, and read/write protection of the module will not be introduced.

### 3.4.1 Read Flash

Flash memory can be directly addressed and reading Flash is affected by the following configuration:

#### Latency

The number of wait states should be configured for different system clocks:

• 0 wait state: 0<system clock≤24MHz

• 1 wait state: 24MHz<system clock≤48MHz

#### Prefetch buffer

It can improve the reading speed and the prefetch buffer will be automatically opened while it is reset; the read interface with prefetch buffer is 2×64 bits for APM32F003x4x6 series. It can be turned on or turned off only when the system clock is consistent with AHB clock and is less than 24MHz.

#### Half-cycle access

When the power consumption needs to be optimized, half-cycle access can be used; at this time, the system clock and AHB clock are consistent, and the system clock is 8MHz or less than 8MHz, then half-cycle access to Flash can be used; otherwise, it must be turned on.

### 3.4.2 Main memory block

#### 3.4.2.1 Main memory block of erase

FMC supports page erase and mass erase (erase all) to initialize the contents of the main memory area to high level (the data is represented as 0xFFFF). Before writing to Flash, users are advised to erase the write address page. If the data of write address is not 0xFFFF, a programming error will be triggered.

#### Main memory page erase

Page erase is an independent erase according to the main memory area page selected by the program, which will not have any impact on the page not selected for erasure.

After the correct page erase (or flash write operation) is completed, OCF of FLASH\_STS register will be set. If OCIE interrupt is enabled, an operation completion interrupt will be triggered. Users need to pay attention that the page selected for erasure must be a valid page (the valid address of the main memory area and the address not write-protected).

#### Main memory mass erase

The mass erase operation will erase all the contents in the main storage area of Flash, and the mass erase operation will erase all the data in the main memory area, so the users need to pay special attention when using it to avoid the loss of important data caused by misoperation.

#### 3.4.2.2 Main memory block of write

FMC supports the writing of 16-bit (half word) data in the main memory area. You can select Debug, BootLoader, program running in SRAM, and directly reading the erased page to judge whether the erasing is successful.

In order to ensure correct writing, it is necessary to check whether the destination address has been erased before writing; if it is not erased, the written data will be invalid and PEF bit of FLASH\_STS register will be set to "1". If the destination address has write protection, the written data is invalid and a write protection error will be triggered (WPEF bit of FLASH\_STS is set to "1").

#### 3.4.2.3 Main memory block of read/write protection

Read/Write protection of the flash is used to prevent invalid reading/modification of the main memory area code or data, and it is controlled by the read/write protection configuration byte of option byte. For APM32F003x4x6 series products, the basic unit of read/write protection is 4 pages (i.e. 4KBytes).

### **Read protection**

Internal Flash protection level can be set by modifying the value of option byte

READPROT. The debugger is always connected to JTAG/SWD interface to set read protection, which takes effect after power-on reset; otherwise, it will not take effect after the system is powered on and reset. When the READPROT value is any value except 0xA5, read protection is enabled and the content of main memory block cannot be read; when the READPROT value is 0xA5, the protection is removed and the content of main memory block can be read; when the read protection is removed, a main memory mass erase operation will be triggered to prevent illegal read after the protection is degraded.

#### Write protection

Write protection control can be conducted for the corresponding page of the main memory block by configuring the value of write protection option byte WRP0/1/2/3. After the write protection is turned on, the content on the corresponding page of the main memory area cannot be modified in any way.

#### 3.4.2.4 Unlock/Lock main memory block

FLASH\_CTRL1 of the reset FMC will be locked by hardware, then FLASH\_CTRL1 cannot be directly written, and the corresponding value must be written to FLASH\_KEY according to the correct sequence to unlock FMC.

Keyword 1=0x45670123

Keyword 2=0xCDEF89AB

The wrong writing sequence or wrong value will cause the program to enter the hardware wrongly. At this time, FMC will be locked, and all FMC operations will be invalid until it is reset next time. The users can also lock FMC through software by writing "1" to LOCK bit of the control register 2 (FLASH\_CTRL2).

In each Flash programming operation, the users must follow the steps of "Flash unlock - program by user - Flash lock", so as to avoid the risk that user code/data is accidentally modified due to the Flash unlocking after the Flash programming operation.

### 3.4.3 Option byte

#### 3.4.3.1 Erase option byte

It supports the erase function. After erasing of the correct option byte, it needs to be reset to take effect.

### **Configuration steps**

- (1) Check BUSYF bit of FLASH\_STS register to confirm no other flash operation is ongoing;

- (2) Set OBWEN bit in FLASH CTRL2 register;

- (3) Set OBE bit in FLASH\_CTRL2 register;

- (4) Set STA bit in FLASH CTRL2 register;

- (5) Wait for BUSYF to be reset;

- (6) Read out the erased option byte and verify it.

### 3.4.3.2 Write option byte

9 configurable bytes of option bytes all support writing function. After the option byte is configured, it needs to be reset to take effect.

#### **Configuration steps**

- (1) Check BUSYF bit of FLASH\_STS register to confirm no other flash operation is ongoing;

- (2) Set OBWEN bit in FLASH\_CTRL2 register;

- (3) Set OBP bit in FLASH\_CTRL2 register;

- (4) Write the half word to be programmed to the specified address;

- (5) Wait for BUSYF to be reset;

- (6) Read the written value and verify it.

#### 3.4.3.3 Option byte of write protection

By default, the option byte is always readable and write protected. To perform write operation (program/erase) for the option byte block, first write the correct key sequence (the same as that of locking) in FLASH\_OBKEY, and then allow the write operation of option byte block; the OBWEN bit of FLASH\_CTRL2 register indicates write enabled; clear this bit and write operation will be disabled.

#### 3.4.3.4 Unlock/Lock option byte

After the system reset, the option byte is locked by default. Only when the option byte is unlocked correctly, can it be modified. To unlock the option byte, the keyword shall be written to the FLASH\_OBKEY register to unlock. The option byte does not support "software lock". The user should pay special attention to that every time the value of the option byte is modified, the system must be reset to make it take effect.

### 3.5 Option byte register functional description

The option byte provides some optional functions for users, and it mainly consists of 8 configurable bytes and corresponding complementary codes. Every time the system is reset, the option byte area will be reloaded to the FLASH\_OBCS and FLASH\_WRTPROT registers (the option byte will only take effect each time they are reloaded to FMC). In the process of reloading, if a certain configurable byte does not match its inverse code, an option byte error (OBE bit of FLASH\_OBCS register is set to "1") will be triggered, and this byte will be set to "0xFF". The information of 24 bytes in the option byte area is shown in the table below.

### Table 5 Option Bytes

| Address     | Option byte | Initial       | R/W | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|-------------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0002 0400 | READPROT    | value<br>0xA5 | R/W | Read protection configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0x0002 0401 | nREADPROT   | 0x5A          | R   | READPROT complementary code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0x0002 0401 | USER        | 0xFF          | R/W | User option byte Bit 0: WWDTSW  0: Hardware watchdog 1: Software watchdog Bit 1: WWDTRST  0: Reset is generated in HALT mode when the window watchdog is valid  1: No reset is generated in HALT mode when the window watchdog is valid Bit 2: IWDTSW  0: Hardware activates the independent watchdog 1: Software activates the independent watchdog Bit 3: LIRCEN  0: LIRC clock can be taken as CPU clock source 1: LIRC clock cannot be taken as CPU clock source Bit 4: HIRCTRIM  0: HIRCTRIM register has 4-bit adjustment value 1: HIRCTRIM register has 3-bit adjustment value [5:7]: Reserved |

| 0x0002 0403 | nUSER       | 0x00          | R   | USER complementary code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0x0002 0404 | Data0       | 0xFF          | R/W | User data byte 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x0002 0405 | nData0      | 0x00          | R   | Data0 complementary code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0x0002 0406 | Data1       | 0xFF          | R/W | User data byte 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x0002 0407 | nData1      | 0x00          | R   | Data complementary code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0x0002 0408 | WRP0        | 0xFF          | R/W | Write protection configuration 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x0002 0409 | nWRP0       | 0x00          | R   | WRP0 complementary code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0x0002 040A | WRP1        | 0xFF          | R/W | Write protection configuration 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x0002 040B | nWRP1       | 0x00          | R   | WRP1 complementary code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0x0002 040C | WRP2        | 0xFF          | R/W | Write protection configuration 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x0002 040D | nWRP2       | 0x00          | R   | WRP2 complementary code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             | WRP3        | 0xFF          | R/W | Write protection configuration 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Address     | Option byte | Initial<br>value | R/W | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|-------------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0002 040F | nWRP3       | 0x00             | R   | WRP3 complementary code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0x0002 0410 | AFR         | -                | R/W | Multiplex mapping option x of bit x, namely, AFRx. Multiplex mapping option 0: 0: Port C5 is multiplexed to TMR2_CH1; Port C6 is multiplexed to TMR1_CH1; Port C7 is multiplexed to TMR1_CH2 1: The mapping option is invalid, and it is multiplexed by default  Multiplex mapping option 1: 0: Port A3 is multiplexed to SPI_NSS; Port D2 is multiplexed to TMR2_CH3 1: The mapping option is invalid, and it is multiplexed by default  Multiplex mapping option 2: Reserved  Multiplex mapping option 3: 0: Port C3 is multiplexed to TLI 1: The mapping option is invalid, and it is multiplexed by default  Multiplex mapping option 4: 0:: Port B4 is multiplexed to ADC_ETR; Port B5 is multiplexed to TMR1_BKIN 1: The mapping option is invalid, and it is multiplexed by default  Multiplex mapping option 5: 0: Port D5 is multiplexed to TMR1A_CH1N; Port D6 is multiplexed to TMR1A_CH2N 1: The mapping option is invalid, and it is multiplexed by default  Multiplex mapping option is invalid, and it is multiplexed by default  Multiplex mapping option 6: Reserved  Multiplex mapping option 7: 0: Port C3 is multiplexed to TMR1_CH1N; Port C4 is multiplexed to TMR1_CH1N; Port C4 is multiplexed to TMR1_CH2N 1: The mapping option is invalid, and |

| Address     | Option byte   | Initial<br>value | R/W   | Functional Description                                                                                                                                                                                                                                                                                                                                          |

|-------------|---------------|------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |               |                  |       | Note: More than one remapping option cannot be enabled on the same port (e.g. AFR0 and AFR1 cannot be enabled at the same time)                                                                                                                                                                                                                                 |

| 0x0002 0411 | nAFR          | -                | R     | AFR complementary code                                                                                                                                                                                                                                                                                                                                          |

| 0x0002 0412 |               |                  | Reser |                                                                                                                                                                                                                                                                                                                                                                 |

| 0x0002 0413 |               |                  | Reser | rved                                                                                                                                                                                                                                                                                                                                                            |

| 0x0002 0414 | HXTCNT        | 0xFF             | R/W   | Bit [0:7]: HXTCNT 0x1E: 0.5 HXT cycles 0x2D: 8 HXT cycles 0x4B: 128 HXT cycles 0xFF: 2048 HXT cycles                                                                                                                                                                                                                                                            |

| 0x0002 0415 | nHXTCNT       | 0x00             | R     | HXTCNT complementary code                                                                                                                                                                                                                                                                                                                                       |

| 0x0002 0416 | CLOCK_OPTION  | 0xFF             | R/W   | User option byte Bit [0:1]: WUPTDIV 00: 4 MHz to 128 kHz prescaler 01: 8 MHz to 128 kHz prescaler 1x: 16 MHz to 128 kHz prescaler Bit 2: WUPTLIRC 0: Select HXT frequency divider as clock source 1: Select LSI frequency divider as clock source Bit 3: EXTCLK 0: External clock signal on OSCIN 1: External crystal connected to OSCIN/OSCOUT [4:7]: Reserved |

| 0x0002 0417 | nCLOCK_OPTION | 0x00             | R     | CLOCK_OPTION complementary code                                                                                                                                                                                                                                                                                                                                 |

Note: When the configurable byte and its complementary code value are "0xFF", the match will not be verified in the reloading process

# 3.6 Register address mapping

Base address: 0x4001 1000

Table 6 Register Address Mapping

|               | - 11 5                   |                |

|---------------|--------------------------|----------------|

| Register name | Description              | Offset address |

| FLASH_CTRL1   | Control register 1       | 0x00           |

| FLASH_KEY     | Key register             | 0x04           |

| FLASH_OBKEY   | Option byte key register | 0x08           |

| FLASH_STS     | State register           | 0x0C           |

| Register name | Description                        | Offset address |

|---------------|------------------------------------|----------------|

| FLASH_CTRL2   | Control register 2                 | 0x10           |

| FLASH_ADDR    | Address register                   | 0x14           |

| FLASH_OBCS    | Option byte control/state register | 0x1C           |

| FLASH_WRTPROT | Write protection register          | 0x20           |

| FLASH_LPM     | Low-power mode register            | 0x24           |

| FLASH_TPO     | Flash tpower_on register           | 0x28           |

# 3.7 Register functional description

### 3.7.1 Control register 1 (FLASH\_CTRL1)

Offset address: 0x00 Reset value: 0x0000 0030

|       | Treest value. Choose coo |       |                                                                  |  |  |

|-------|--------------------------|-------|------------------------------------------------------------------|--|--|

| Field | Name                     | R/W   | Description                                                      |  |  |

|       |                          |       | Latency Status Configure                                         |  |  |

| 2:0   | LATENCY                  | R/W   | 000: 0 wait state, 0 <system clock≤24mhz<="" td=""></system>     |  |  |

| 2.0   | LATENCT                  | 17/// | 001: 1 wait state: 24MHz <system clock≤48mhz<="" td=""></system> |  |  |

|       |                          |       | Others: Reserved                                                 |  |  |

|       |                          |       | Flash Half Cycle Access Enable                                   |  |  |

| 3     | HCAEN                    | R/W   | 0: Disable                                                       |  |  |

|       |                          |       | 1: Enable                                                        |  |  |

|       |                          |       | Prefetch Buffer Enable                                           |  |  |

| 4     | PBEN                     | R/W   | 0: Disable                                                       |  |  |

|       |                          |       | 1: Enable                                                        |  |  |

|       |                          |       | Prefetch Buffer Status Flag                                      |  |  |

| 5     | PBSF                     | R     | 0: In closed state                                               |  |  |

|       |                          |       | 1: In open state                                                 |  |  |

| 31:6  |                          |       | Reserved                                                         |  |  |

### 3.7.2 Key register 1 (FLASH\_KEY)

Offset address: 0x04

Reset value: 0xXXXX XXXX

| Field | Name | R/W | Description                                                                                                                                                         |

|-------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0  | KEY  | W   | FMC Key Writing the keys represented by these bits can unlock FMC. These bits can only perform write operation, and 0 is returned when read operation is performed. |

### 3.7.3 Option byte key register (FLASH\_OBKEY)

Offset address: 0x08

Reset value: 0x03FF FFFC

The reset value of the register is related to the value written in the option byte; the reset value of OBE bit is related to the result of comparison between the loaded option byte and its inverse code.

| Field | Name | R/W | Description                                                                                                                                                                                            |

|-------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0  | KEY  | W   | Option Byte Key Writing the keys represented by these bits can unlock the option byte write operation. These bits can only perform write operation and 0 is returned when read operation is performed. |

### 3.7.4 State register (FLASH\_STS)

Offset address: 0x0C Reset value: 0x0000 0000

| Field | Name     | R/W | Description                                                                                                                                                           |  |

|-------|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0     | BUSYF    | R   | Busy Flag  This bit indicates that a flash operation is in progress. These bits can only perform write operation, and 0 is returned when read operation is performed. |  |

| 1     |          |     | Reserved                                                                                                                                                              |  |

| 2     | PEF      | R/W | Programming Error Flag  This bit will be set by software when the value before the address is edited is not "0xFFFF".                                                 |  |

| 3     | Reserved |     |                                                                                                                                                                       |  |

| 4     | WPEF     | R/W | Write Protection Error Flag This bit will be set by hardware when programming the write protection address in FLASH.                                                  |  |

| 5     | OCF      | R/W | Operation Complete Flag This bit will be set by hardware when read/write operation in FLASH is completed.                                                             |  |

| 31:6  |          |     | Reserved                                                                                                                                                              |  |

# 3.7.5 Control register 2 (FLASH\_CTRL2)

Offset address: 0x10 Reset value: 0x0000 0080

| Field | Name     | R/W | Description                                                       |

|-------|----------|-----|-------------------------------------------------------------------|

| 0     | PG       | R/W | Program Set this bit to 1 to program Flash.                       |

| 1     | PAGEERA  | R/W | Page Erase Set this bit to 1 to erase the page                    |

| 2     | MASSERA  | R/W | Mass Erase Set this bit to 1 to erase the mass.                   |

| 3     | Reserved |     |                                                                   |

| 4     | OBP      | R/W | Option Byte Program Set this bit to 1 to program the option byte. |

| 5     | OBE      | R/W | Option Byte Erase Set this bit to 1 to erase the option byte.     |

| Field | Name     | R/W | Description                                                                                                                                                                                   |

|-------|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6     | STA      | R/W | Start Erase  This bit can be only set to 1 by software, and can be reset by clearing BUSYF bit of STS register.                                                                               |

| 7     | LOCK     | R/W | Lock This bit can be written to 1 only, and when it is set to 1, it means that Flash and CTRL2 registers are locked.                                                                          |

| 8     |          |     | Reserved                                                                                                                                                                                      |

| 9     | OBWEN    | R/W | Option Byte Write Enable When this bit is set to 1, the option byte can be programmed.                                                                                                        |

| 10    | ERRIE    | R/W | Error interrupt Enable  0: Disable interrupt  1: Enable interrupt  When PEF=1 or WPEF=1 for the STS register, set this bit to generate an interrupt.                                          |

| 11    |          |     | Reserved                                                                                                                                                                                      |

| 12    | OCIE     | R/W | Operation Complete Interrupt Enable  0: Disable operation completion interrupt  1: Enable operation completion interrupt  When OCF=1 for STS register, set this bit to generate an interrupt. |

| 31:13 | Reserved |     |                                                                                                                                                                                               |

### 3.7.6 Address register (FLASH\_ADDR)

Offset address: 0x14

Reset value: 0x0000 0000

The register is changed to currently/finally used address by hardware; in page erase, the register needs to be configured by software.

| Field | Name | R/W | Description                                                                                                                                              |

|-------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0  | ADDR | W   | Flash Address In programming operation, the bit is written to the address to be programmed; in page erase, this bit is written to the page to be erased. |

### 3.7.7 Option bye control/state register (FLASH\_OBCS)

Offset address: 0x1C

Reset value: 0x03FF FFFC

The reset value of the register is related to the value written in the option byte; the reset value of OBE bit is related to the result whether the value of the loaded option byte is consistent with its inverse code.

| Field | Name     | R/W | Description                                                                                                                                                 |

|-------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | OBE      | R   | Option Byte Error  1: The loaded option byte does not match its complementary code.  The option byte and its complementary code are forced to write to 0xFF |

| 1     | READPROT | R   | Read Protect 1: Indicate that the flash memory is in read protection state                                                                                  |

| Field | Name     | R/W | Description                                                                                                         |  |  |

|-------|----------|-----|---------------------------------------------------------------------------------------------------------------------|--|--|

| 2     | WWDTSW   | R   | WWDT Switch 0: Hardware activates the window watchdog 1: Software activates the window watchdog                     |  |  |

| 3     | WWDTRST  | R   | WWDT Reset This bit controls the window watchdog to generate reset in HALT mode. 0: Generate 1: Not generate        |  |  |

| 4     | IWDTSW   | R   | IWDT Switch 0: Hardware activates the independent watchdog 1: Software activates the independent watchdog           |  |  |

| 5     | LIRCEN   | R   | LIRC Enable 0: LIRC clock can be taken as CPU clock source 1: LIRC clock cannot be taken as CPU clock source        |  |  |

| 6     | HIRCTRIM | R   | HIRC Trim This bit controls the bit number of adjustment values that the HIRCTRIM register has. 0: 4 bits 1: 3 bits |  |  |

| 9:7   | Reserved |     |                                                                                                                     |  |  |

| 17:10 | DATA0    | R   | Data0                                                                                                               |  |  |

| 25:18 | DATA1    | R   | Data1                                                                                                               |  |  |

| 31:26 | Reserved |     |                                                                                                                     |  |  |

# 3.7.8 Write protection register (FLASH\_WRTPROT)

Offset address: 0x20 Reset value: 0xFFFF FFFF

Field Name R/W Description

31:0 WRTPROT R 0: Valid

1: Invalid

### 3.7.9 Low-power mode register (FLASH\_LPM)

Offset address: 0x24 Reset value: 0x0000 0000

| Field | Name  | R/W | Description                                                                                                                                                                                                          |

|-------|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | HALT  | R/W | Flash is Power-down in Halt mode This bit is set to 1 or cleared to 0 by software.  0: When MCU is in halt mode, Flash is power-down.  1: When MCU is in halt mode, Flash is in working state.                       |

| 1     | AHALT | R/W | Flash is Power-down in Active-halt mode  This bit is set to 1 or cleared to 0 by software.  0: When MCU is in Active-halt mode, Flash is in working state.  1: When MCU is in Active-halt mode, Flash is power-down. |

| Field | Name | R/W | Description |

|-------|------|-----|-------------|

| 31:2  |      |     | Reserved    |

# 3.7.10 Flash tpower\_on register (FLASH\_TPO)

Offset address: 0x28

Reset value: 0x0000 0000

| Field | Name     | R/W | Description                                                                                                                       |

|-------|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------|

| 7:0   | TPO      | R/W | The t <sub>su</sub> of Flash in Power-down mode When Flash starts from power-down mode, it needs to wait for 2us to run normally. |

| 31:8  | Reserved |     |                                                                                                                                   |

# 4 Power Management Unit (PMU)

### 4.1 Full Name and Abbreviation Description of Terms

Table 7 Full Name and Abbreviation Description of Terms

| Full name in English | English abbreviation |

|----------------------|----------------------|

| Power On Reset       | POR                  |

| Power Down Reset     | PDR                  |

### 4.2 Introduction

The power supply is the foundation for stable operation of a system, with working voltage of 2.4~5.5V, and 1.5V power supply can be provided through the built-in voltage regulator to digital peripherals.

### 4.3 Structure block diagram

VCAP V<sub>DD</sub> power domain Vcore power domain I/O buffer 2. 4V-5. 5V Core VDD Flash 1. 5V Main voltage regulator SRAM VSS APB digital Low-power voltage regulator peripheral 2. 4V-5. 5V V<sub>DD</sub> power domain VDD VSS A/D converter VREF+ VREF-

Figure 2 Power Supply Control Structure Block Diagram

### 4.4 Functional Description

### 4.4.1 Power domain

The power domain of the product includes:  $V_{DD}$  power domain, and  $V_{Core}$  power domain.

### **4.4.1.1 V**<sub>DD</sub> power domain

$V_{DD}/V_{SS}$  pin can supply power for internal main voltage regulator (MVR), internal low-power voltage regulator (LPVR) and I/O ports, and the voltage range is 2.4~5.5V.

### 4.4.1.2 V<sub>Core</sub> power domain

The main voltage regulator and low-Power voltage regulator supply power for the core, FLASH, RAM and digital peripherals, and the power supply voltage is 1.5V.

### 4.5 Power Management

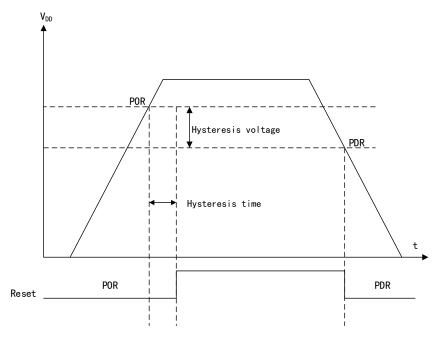

### 4.5.1 Power-on/power-down reset (POR and PDR)

When the  $V_{DD}$  is detected to be lower than the threshold voltage  $V_{POR}$  and  $V_{PDR}$ , the chip will automatically remain in the reset state. The waveform diagrams of power-on reset and power-down reset are as follows. For POR, PDR, hysteresis voltage and hysteresis time, please refer to the "Datasheet".

Figure 3 Power-on Reset and Power-down Reset Oscillogram

#### 4.5.2 Power control

### 4.5.2.1 Reduce the power in low-power mode

There are four low-power modes: wait mode, fast active-halt mode, slow active-halt mode, and halt mode. The power is reduced by closing the core and clock source and setting the voltage regulator.

Table 8 Main Characteristics of Four Low-power Modes

| Mode                    | Wakeup and trigger event                              | CPU | Oscillator                  | Main voltage regulator                             | Peripheral                                       |

|-------------------------|-------------------------------------------------------|-----|-----------------------------|----------------------------------------------------|--------------------------------------------------|

| Wait                    | All internal interrupts or external interrupts, reset | Off | On                          | On                                                 | On <sup>(1)</sup>                                |

| Fast<br>active-<br>halt | WUPT or external (2) interrupt, reset                 | Off | Off except<br>LIRC (or HXT) | On                                                 | Only WUPT and IWDT (if they have been activated) |

| Slow<br>active-<br>halt | WUPT or external (2) interrupt, reset                 | Off | Off except<br>LIRC          | Off (the low-<br>power voltage<br>regulator is on) | Only WUPT and IWDT (if they have been activated) |

| Stop                    | External <sup>(2)</sup> interrupt, reset              | Off | Off                         | Off (the low-<br>power voltage<br>regulator is on) | Off                                              |

Note: 1. If peripheral clock is not turned off

2. Include interrupt of communication peripheral (SPI, I2C) (see the interrupt vector table)

### Wait mode

Table 9 Characteristics of Wait Mode

| Characteristics | Description                                                                       |

|-----------------|-----------------------------------------------------------------------------------|

| Enter           | Enter the wait mode by executing WFI instruction                                  |

| Wakeup          | Wake up by any interrupt                                                          |

| During waiting  | The core stops running, peripherals and interrupt controllers remain running, and |

| During waiting  | all registers, RAM and defined clock configurations remain unchanged              |

| Wakeup delay    | None                                                                              |

### Halt mode

Table 10 Characteristics of Halt Mode

| Characteristics | Description                                                                       |  |  |

|-----------------|-----------------------------------------------------------------------------------|--|--|

| Enter           | Enter the halt mode by executing HALT instruction                                 |  |  |

| Wakeup          | Wake up by internal interrupt                                                     |  |  |

|                 | The master clock, CPU and peripherals stop running, the contents of all registers |  |  |

| Halt            | and RAM remain unchanged, the clock configuration remains unchanged by            |  |  |

|                 | default, and the low voltage regulator is in working state                        |  |  |

| Wakaun dalay    | Wakeup time of master clock + voltage regulator wakeup time from low-power        |  |  |

| Wakeup delay    | mode                                                                              |  |  |

### **Active-halt**

Table 11 Characteristics of Active-halt Mode

| Characteristics                                | Description                                                                 |

|------------------------------------------------|-----------------------------------------------------------------------------|

| Enter                                          | First enable WUPT and then enter the active-halt mode by executing HALT     |

| Enter                                          | instruction                                                                 |

| Wakeup Wake up automatically by internal event |                                                                             |

|                                                | The main oscillator, CPU and peripherals stop running. If WUPT and IWDT are |

| Active-halt                                    | enabled, only LIRC and HXT are running to drive the counters of WUPT and    |

|                                                | IWDT.                                                                       |

| Makaus dalau                                   | Wakeup time of master clock + voltage regulator wakeup time from low-power  |

| Wakeup delay                                   | mode (FLASH is always working, which can reduce the wakeup time)            |

### 4.5.2.2 Reduce the power in run mode

In run mode, the power can be reduced by reducing the system clock, turning off unused peripherals and turning off all unused analog function blocks.

### 5 Auto Wakeup (WUPT)

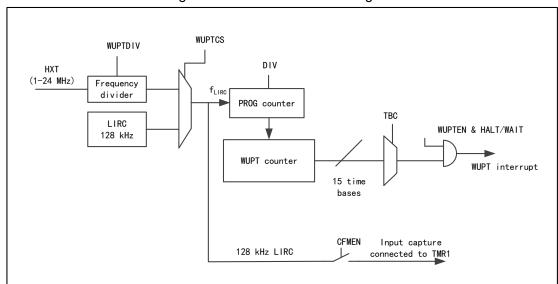

### 5.1 Introduction

WUPT can provide an internal wakeup time reference when MCU enters low-power active-halt mode. The clock of the time reference is provided by the internal low-speed RC oscillator clock (LIRC) or the HXT crystal oscillator clock of prescaler.

### 5.2 Structure block diagram

Figure 4 WUPT Clock Block Diagram

### 5.3 Functional Description

### 5.3.1 WUPT configuration process

- Set CFMEN bit of the configuration register WUPT\_CSTS to 1 to connect LIRC to the input capture channel 1 of TMR1

- Define appropriate prescaler value by DIV[5:0] bit of the configuration register WUPT DIV

- Select required automatic wakeup delay through TBC[3:0] bit of the configuration register WUPT TBC

- Enable WUPT function through WUPTEN bit of the configuration register WUPT CSTS

- Execute HALT instruction

### 5.3.2 LIRC clock frequency detection

In order to obtain accurate automatic wakeup time interval or buzzer output, it is necessary to accurately measure the LIRC frequency

The clock frequency detection steps are as follows:

- Set CFMEN bit of the configuration register WUPT\_CSTS to 1 to connect LIRC to the input capture channel 1 of TMR1

- Measure the frequency of LIRC through input capture interrupt of the timer

### 5.3.3 Time base selection

The time interval of WUPT depends on: output column of counter given by TBC [3:0] bit and prescaler factor given by DIV [5:0] bit. 15 non-overlapping time intervals can be defined, as shown in the following table:

Table 12 TBC[3:0] Selection

| TBC[3:0] | Time interval                                                                  | DIV range |

|----------|--------------------------------------------------------------------------------|-----------|

| 0001     | 2/f <sub>LIRC</sub> -64/f <sub>LIRC</sub>                                      | 2 to 64   |

| 0010     | 2×32/f <sub>LIRC</sub> -2×64/f <sub>LIRC</sub>                                 | 32 to 64  |

| 0011     | 2×2×32/ f <sub>LIRC</sub> -2 <sup>2</sup> ×64/f <sub>LIRC</sub>                | 32 to 64  |

| 0100     | 2×2 <sup>2</sup> ×32/f <sub>LIRC</sub> -2 <sup>3</sup> ×64/f <sub>LIRC</sub>   | 32 to 64  |

|          |                                                                                |           |

| 1100     | 2×2 <sup>10</sup> ×32/f <sub>LIRC</sub> -2 <sup>11</sup> ×64/f <sub>LIRC</sub> | 32 to 64  |

| 1101     | 2×2 <sup>11</sup> ×32/f <sub>LIRC</sub> -2 <sup>12</sup> ×64/f <sub>LIRC</sub> | 32 to 64  |

| 1110     | 2 <sup>11</sup> ×130/f <sub>LIRC</sub> -2 <sup>11</sup> ×320/f <sub>LIRC</sub> | 26 to 64  |

| 1111     | 2 <sup>11</sup> ×330/f <sub>LIRC</sub> -2 <sup>12</sup> ×960/f <sub>LIRC</sub> | 11 to 64  |

The user can determine the value of WUPTTBC [3:0] according to the desired time interval, and then select the value of the corresponding DIV [5:0].

# 5.4 Register address mapping

Table 13 Register Address Mapping

| Register name | Description                          | Offset address |

|---------------|--------------------------------------|----------------|

| WUPT_CSTS     | WUPT control state register          | 0x00           |

| WUPT_DIV      | WUPT asynchronous prescaler register | 0x04           |

| WUPT_TBC      | WUPT time base selection register    | 0x08           |

# 5.5 Register functional description

### 5.5.1 WUPT control state register (WUPT CSTS)

Offset address: 0x00 Reset value: 0x0000 0000

| Field | Name                                                                                                                                                                                                                            | R/W                                                                                                                                                                                                                                                      | Description                   |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--|--|

| 0     | CFMEN                                                                                                                                                                                                                           | R/W                                                                                                                                                                                                                                                      | Measurement Enable 0: Disable |  |  |

| 3:1   |                                                                                                                                                                                                                                 | 1: Enable  Reserved                                                                                                                                                                                                                                      |                               |  |  |

| 4     | WUPTEN                                                                                                                                                                                                                          | Auto-wakeup Enable This bit is set to 1 and cleared to 0 by the software. If the MCU enters the active-halt or wait mode, the automatic wakeup module will be programmed in advance to wake up the MCU after a certain time delay.  0: Disable 1: Enable |                               |  |  |

| 5     | Auto-wakeup Interrupt Flag  This bit is cleared when performing read operation to WUPT_CST register, but write operation is invalid.  0: No automatic wakeup interrupt is generated  1: Automatic wakeup interrupt is generated |                                                                                                                                                                                                                                                          |                               |  |  |

| 31:6  | Reserved                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                          |                               |  |  |

# 5.5.2 WUPT asynchronous prescaler register (WUPT\_DIV)

Offset address: 0x04 Reset value: 0x0000 00C0

| Field | Name     | R/W | Description                                                                                                                                                                                                                                                                                                                                 |  |

|-------|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 5:0   | DIV      | R/W | Asynchronous Prescaler Value Select This bit is used to select the prescaler value provided to the counter clock.  00h: 2 divided frequency 01h: 3 divided frequency 06h: 8 divided frequency 0Eh: 16 divided frequency 0Fh: 17 divided frequency 3Eh: 64 divided frequency Note: This register cannot set to the initial reset value (3Fh) |  |

| 31:6  | Reserved |     |                                                                                                                                                                                                                                                                                                                                             |  |

### 5.5.3 WUPT time base selection register (WUPT\_TBC)

Offset address: 0x08 Reset value: 0x0000 0000

| Field | Name | R/W | Description                                                                                                                                                        |  |  |  |  |

|-------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 3:0   | TBC  | R/W | Auto-wakeup Timebase Select This bit is used to define the automatic wakeup interrupt time.  0000: No automatic wakeup interrupt  0001: C=1  0100: C=2  0011: C=2² |  |  |  |  |

| Field | Name     | R/W | Description                                               |

|-------|----------|-----|-----------------------------------------------------------|

|       |          |     | 0100: C=2 <sup>3</sup>                                    |

|       |          |     | 0101: C=2 <sup>4</sup>                                    |

|       |          |     | 0110: C=2 <sup>5</sup>                                    |

|       |          |     | 0111: C=2 <sup>6</sup>                                    |

|       |          |     | 1000: C=2 <sup>7</sup>                                    |

|       |          |     | 1001: C=28                                                |

|       |          |     | 1010: C=2 <sup>9</sup>                                    |

|       |          |     | 1011: C=2 <sup>10</sup>                                   |

|       |          |     | 1100: C=2 <sup>11</sup>                                   |

|       |          |     | 1101: C=2 <sup>12</sup>                                   |

|       |          |     | 1110: C=5×2 <sup>11</sup>                                 |

|       |          |     | 1111: C=30×2 <sup>11</sup>                                |

|       |          |     | C is coefficient; basic duration =C×DIV/f <sub>LIRC</sub> |

| 31:4  | Reserved |     |                                                           |

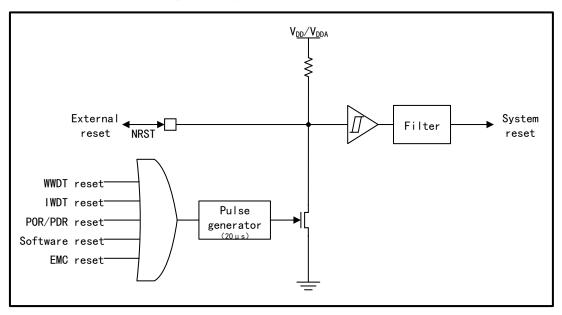

# 6 Reset and Clock (RCM)

### 6.1 Full Name and Abbreviation Description of Terms

Table 14 Full Name and Abbreviation Description of Terms

| Full name in English       | English abbreviation |

|----------------------------|----------------------|

| Reset and Clock Management | RCM                  |

| Reset                      | RST                  |

| Power-On Reset             | POR                  |

| Power-Down Reset           | PDR                  |

| High Speed External Clock  | HXT                  |

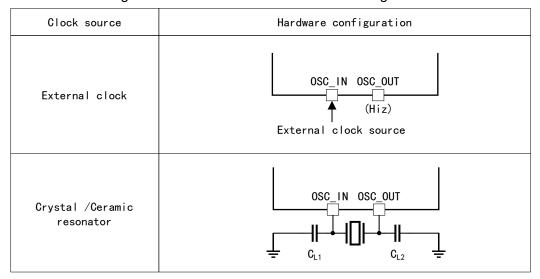

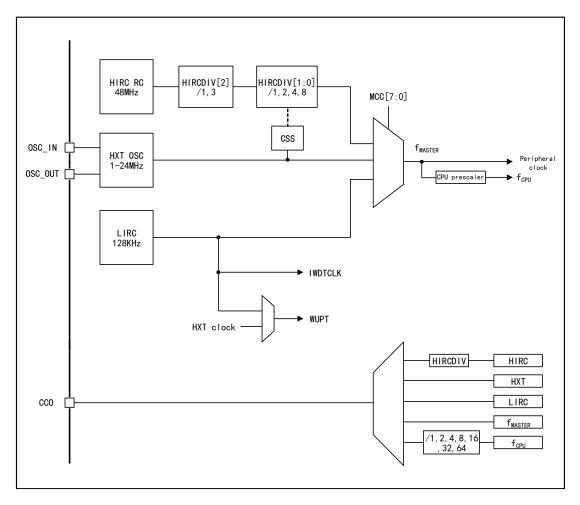

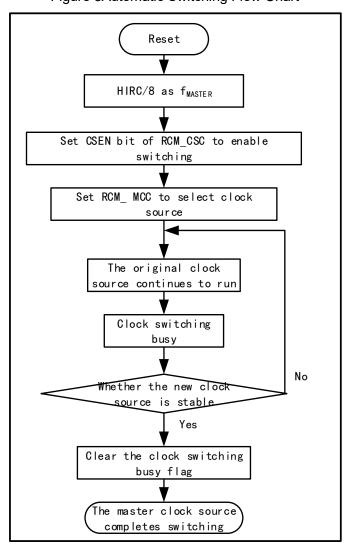

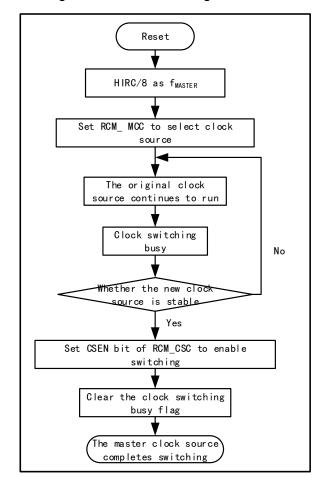

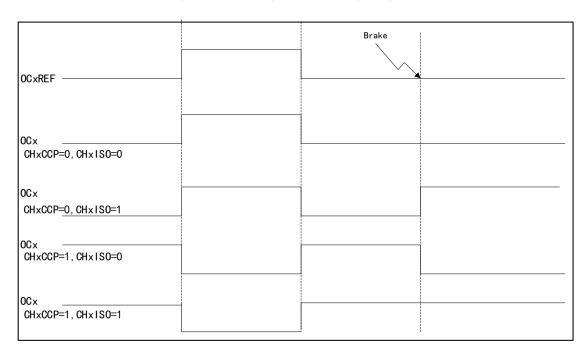

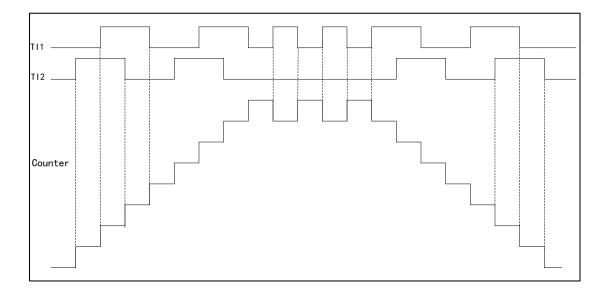

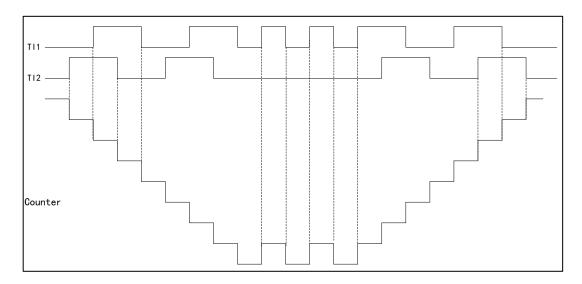

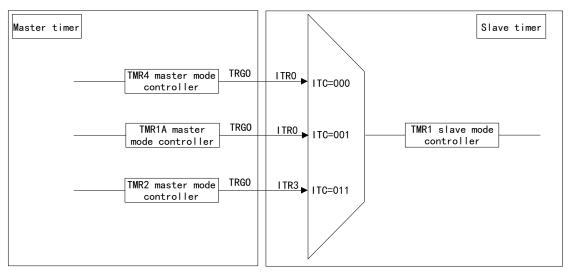

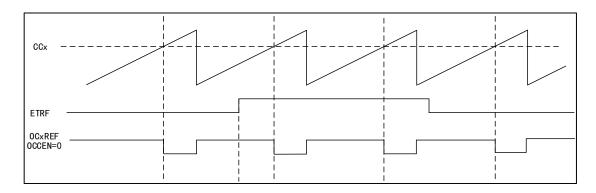

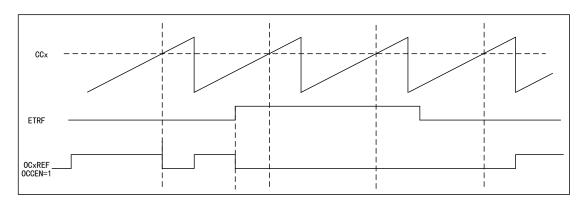

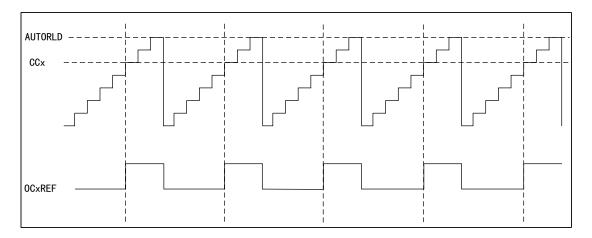

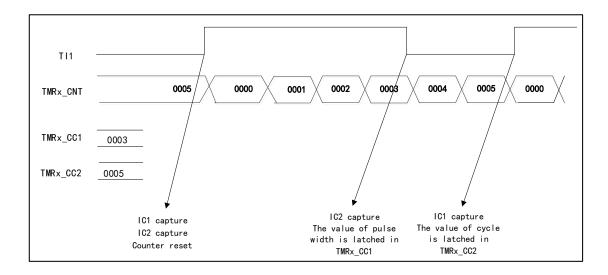

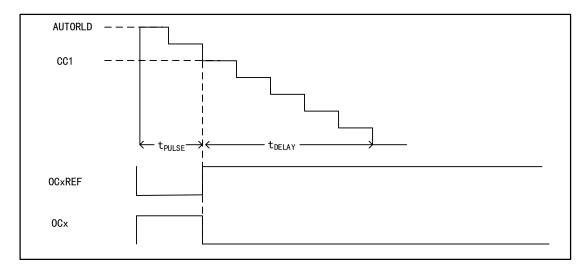

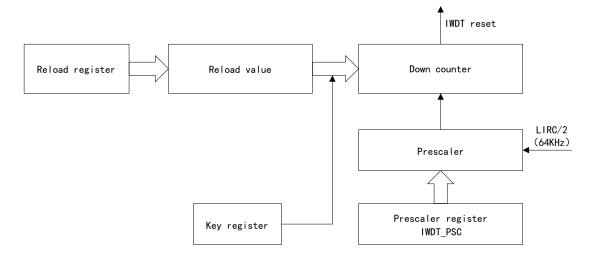

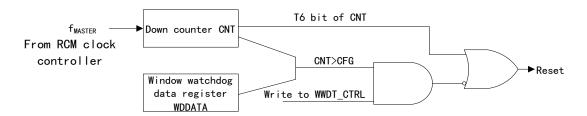

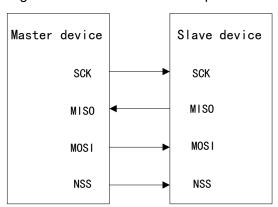

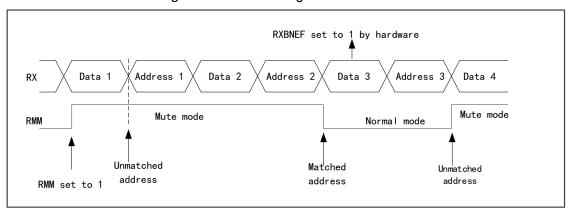

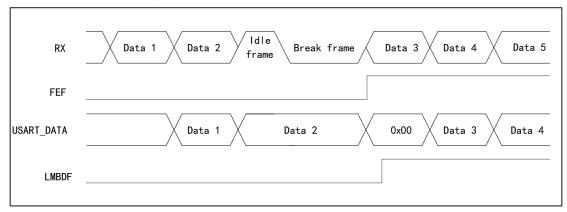

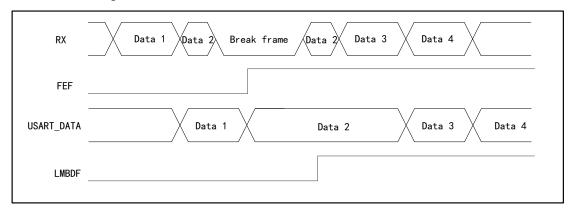

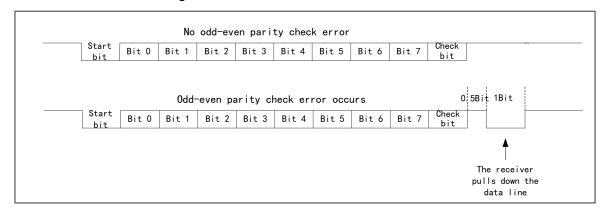

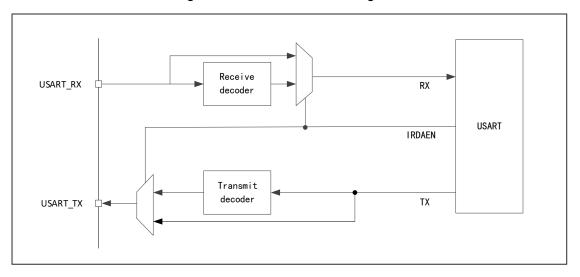

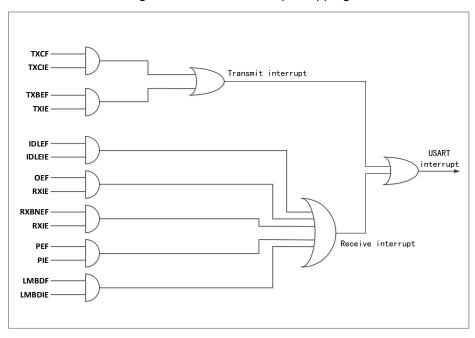

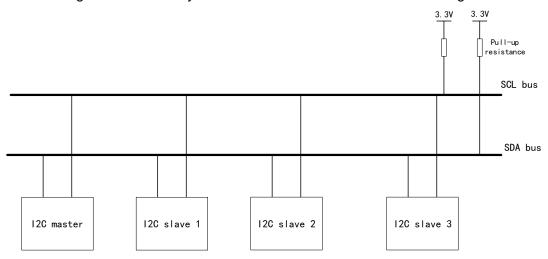

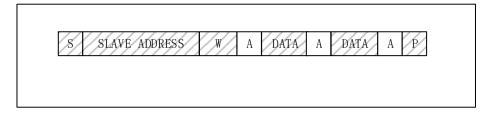

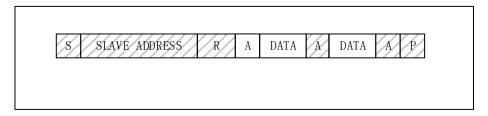

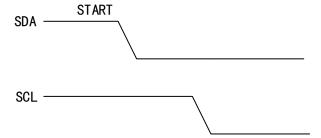

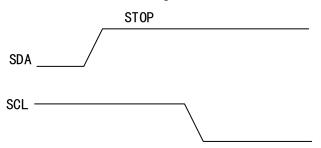

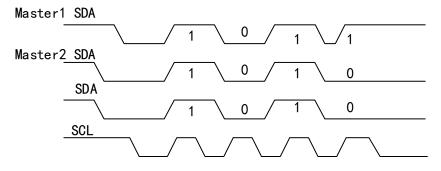

| High Speed Internal Clock  | HIRC                 |